Title: Parity generator & Checker Practical Based on VHDL Programming Aim: To design and verify the truth table of a three bit Odd Parity generator and checker. Objectives: • To study the VHDL programming language. • To study the Parity generator & Checker. Software & Hardware Requirement: • Minimum Pentium 4, 512 MB RAM & 40 HDD.

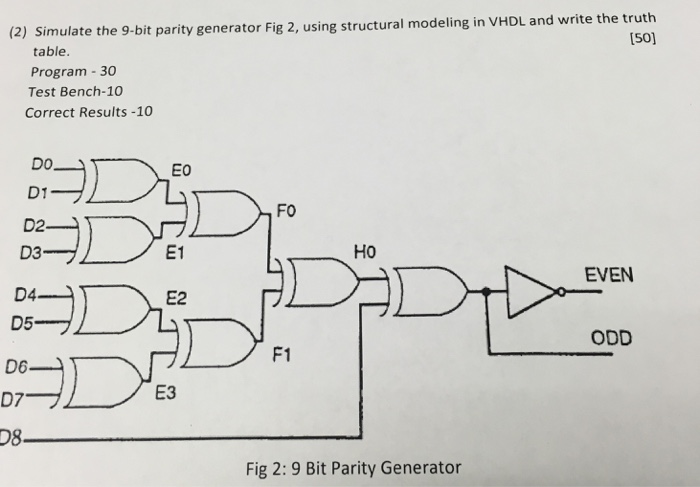

VHDL Code for 9 bit Parity Generator using Structural modelling PROGRAM:. VHDL (42) ELECTRONICS (14).

• Xilinx software version 9.1v. Theory of Parity Generator: A parity bit is used for the purpose of detecting errors during transmission of binary information. A parity bit is an extra bit included with a binary message to make the number of 1’s either odd or even. The message including the parity bit is transmitted and then checked at the receiving end for errors. An error is detected if the checked parity does not correspond with the one transmitted. The circuit that generates the parity bit in the transmitter is called a parity generator and the circuit that checks the parity in the receiver is called a parity checker. Free adjustment program epson p50 download.

In even parity the added parity bit will make the total number of 1’s an even amount and in odd parity the added parity bit will make the total number of 1’s an odd amount. In a three bit odd parity generator the three bits in the message together with the parity bit are transmitted to their destination, where they are applied to the parity checker circuit. The parity checker circuit checks for possible errors in the transmission. Since the information was transmitted with odd parity the four bits received must have an odd number of 1’s.

An error occurs during the transmission if the four bits received have an even number of 1’s, indicating that one bit has changed during transmission. The output of the parity checker is denoted by PEC (parity error check) and it will be equal to 1 if an error occurs, i.e., if the four bits received has an even number of 1’s.

Most Viewed News

- Free Download Game Pc Strategi Perang Kerajaan Islam

- Stilj Programmirovaniya Dzho Selko Na Sql Pdf

- Download Free Microsoft Image Composer 15 Software

- Eyeshield 21 Full Episodes Torrent Download

- Automation Studio 5 Library Files Free

- Lippincott Medical Physiology Pdf

- Download Gratis Desain Undangan Pernikahan Tahun

- Download Lagu Andai Aku Bisa Afgan

- Roum Ru Najti Cheloveka Po Nomeru Telefona

- Jeff Buckley Full Discography Torrent

- Opisanie Vneshnosti Putina Na Anglijskom Yazike

- Happy Birthday To You My Dear Lucky Name Tone Mp3 Song

- Ebook Harry Potter Bahasa Indonesia Lengkap Sdnb

- Naruto Sound Effects Pack Free Download

- Camel Stationary Traveller Mp3